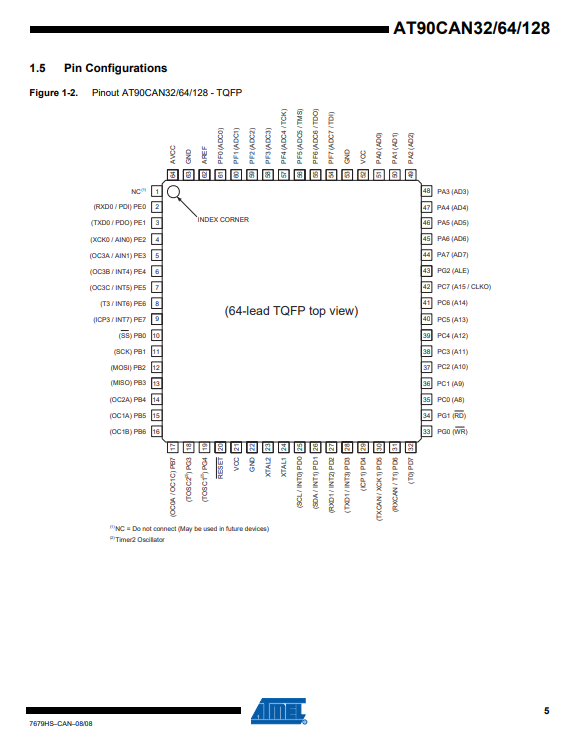

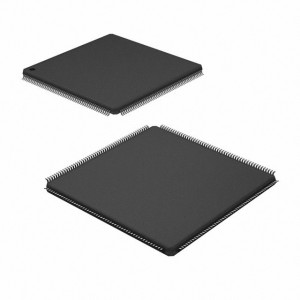

AT90CAN128-16AU IC MCU 8BIT 128KB FLASH 64TQFP

thông số sản phẩm

Sự miêu tả

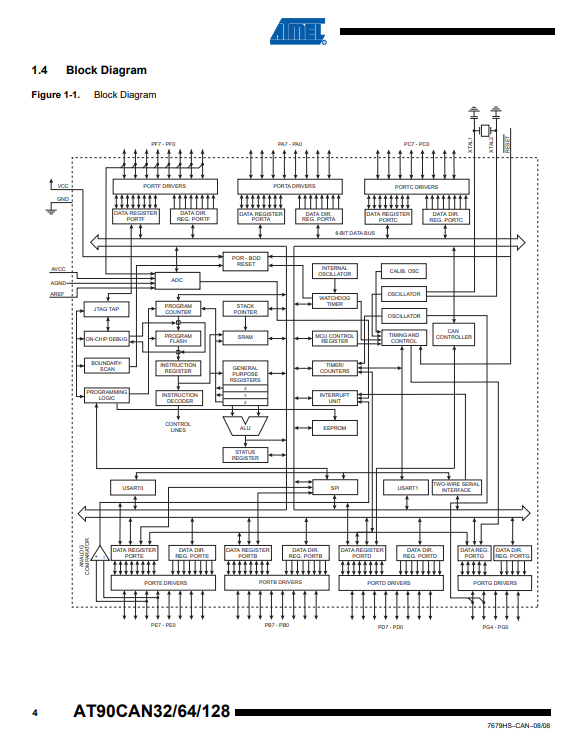

AT90CAN32/64/128 là bộ vi điều khiển CMOS 8-bit công suất thấp dựa trên kiến trúc RISC nâng cao của AVR.Bằng cách thực hiện các hướng dẫn mạnh mẽ trong một chu kỳ xung nhịp duy nhất, AT90CAN32/64/128 đạt được thông lượng gần 1 MIPS trên MHz cho phép nhà thiết kế hệ thống tối ưu hóa mức tiêu thụ điện năng so với tốc độ xử lý.Lõi AVR kết hợp một tập lệnh phong phú với 32 thanh ghi làm việc cho mục đích chung.Tất cả 32 thanh ghi được kết nối trực tiếp với Đơn vị logic số học (ALU), cho phép truy cập hai thanh ghi độc lập trong một lệnh duy nhất được thực thi trong một chu kỳ xung nhịp.Kết quả là kiến trúc mã hiệu quả hơn trong khi đạt được thông lượng nhanh hơn gấp 10 lần so với các bộ vi điều khiển CISC thông thường.AT90CAN32/64/128 cung cấp các tính năng sau: 32K/64K/128K byte Flash có thể lập trình trong hệ thống với khả năng Đọc-While-Write, EEPROM 1K/2K/4K byte, SRAM 2K/4K/4K byte, 53 mục đích chung Các dòng I/O, 32 thanh ghi làm việc cho mục đích chung, bộ điều khiển CAN, Bộ đếm thời gian thực (RTC), bốn Bộ định thời/Bộ đếm linh hoạt với các chế độ so sánh và PWM, 2 USART, Giao diện nối tiếp hai dây định hướng byte, 8 kênh 10 -bit ADC với giai đoạn đầu vào vi sai tùy chọn với mức tăng có thể lập trình, Bộ định thời Watchdog có thể lập trình với Bộ tạo dao động bên trong, cổng nối tiếp SPI, tiêu chuẩn IEEE.Giao diện kiểm tra JTAG tuân thủ 1149.1, cũng được sử dụng để truy cập vào hệ thống và lập trình Gỡ lỗi trên chip và năm chế độ tiết kiệm năng lượng có thể lựa chọn bằng phần mềm.Chế độ Chờ dừng CPU trong khi vẫn cho phép SRAM, Bộ định thời/Bộ đếm, cổng SPI/CAN và hệ thống ngắt tiếp tục hoạt động.Chế độ Tắt nguồn lưu nội dung thanh ghi nhưng đóng băng Bộ tạo dao động, vô hiệu hóa tất cả các chức năng khác của chip cho đến khi có ngắt tiếp theo hoặc Thiết lập lại phần cứng.Ở chế độ Tiết kiệm năng lượng, bộ hẹn giờ không đồng bộ tiếp tục chạy, cho phép người dùng duy trì cơ sở hẹn giờ trong khi phần còn lại của thiết bị đang ở chế độ ngủ.Chế độ Giảm nhiễu ADC dừng CPU và tất cả các mô-đun I/O ngoại trừ Bộ hẹn giờ không đồng bộ và ADC, để giảm thiểu tiếng ồn chuyển đổi trong quá trình chuyển đổi ADC.Ở chế độ Chờ, Bộ tạo dao động tinh thể/Bộ cộng hưởng đang chạy trong khi phần còn lại của thiết bị đang ở chế độ ngủ.Điều này cho phép khởi động rất nhanh kết hợp với mức tiêu thụ điện năng thấp.Thiết bị này được sản xuất bằng công nghệ bộ nhớ không bay hơi mật độ cao của Atmel.Onchip ISP Flash cho phép bộ nhớ chương trình được lập trình lại trong hệ thống thông qua giao diện nối tiếp SPI, bởi bộ lập trình bộ nhớ cố định thông thường hoặc bởi chương trình Khởi động trên chip chạy trên lõi AVR.Chương trình khởi động có thể sử dụng bất kỳ giao diện nào để tải xuống chương trình ứng dụng trong bộ nhớ Flash ứng dụng.Phần mềm trong phần Flash khởi động sẽ tiếp tục chạy trong khi phần Flash ứng dụng được cập nhật, cung cấp hoạt động Đọc-While-Write thực sự.

| thông số kỹ thuật: | |

| Thuộc tính | Giá trị |

| Loại | Mạch tích hợp (IC) |

| Nhúng - Vi điều khiển | |

| mfr | Công nghệ vi mạch |

| Loạt | AVR® 90CAN |

| Bưu kiện | Cái mâm |

| Tình trạng một phần | Tích cực |

| Bộ xử lý lõi | AVR |

| Kích thước lõi | 8 bit |

| Tốc độ | 16 MHz |

| kết nối | CANbus, EBI/EMI, I²C, SPI, UART/USART |

| thiết bị ngoại vi | Brown-out Phát hiện/Đặt lại, POR, PWM, WDT |

| Số lượng I/O | 53 |

| Kích thước bộ nhớ chương trình | 128KB (128K x 8) |

| Loại bộ nhớ chương trình | TỐC BIẾN |

| Kích thước EEPROM | 4K x 8 |

| Kích thước RAM | 4K x 8 |

| Điện áp - Cung cấp (Vcc/Vdd) | 2.7V ~ 5.5V |

| Bộ chuyển đổi dữ liệu | A/D 8x10b |

| Loại dao động | Nội bộ |

| Nhiệt độ hoạt động | -40°C ~ 85°C (TA) |

| Kiểu lắp | Bề mặt gắn kết |

| Gói / Trường hợp | 64-TQFP |

| Gói thiết bị nhà cung cấp | 64-TQFP (14x14) |

| Số sản phẩm cơ sở | AT90CAN128 |

Có liên quanCÁC SẢN PHẨM

-

điện thoại

-

E-mail

-

Ứng dụng trò chuyện

-

whatsapp

whatsapp