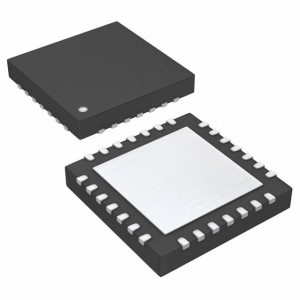

XC2C64A-7VQG100C IC CPLD 64MC 6.7NS 100VQFP

thông số sản phẩm

Sự miêu tả

Thiết bị 64-macrocell CoolRunner-II được thiết kế cho cả ứng dụng hiệu suất cao và tiêu thụ điện năng thấp.Điều này giúp tiết kiệm năng lượng cho các thiết bị liên lạc cao cấp và tốc độ cao cho các thiết bị chạy bằng pin.Do chế độ chờ công suất thấp và hoạt động năng động, độ tin cậy tổng thể của hệ thống được cải thiện.Thiết bị này bao gồm bốn Khối chức năng được kết nối với nhau bằng Ma trận kết nối nâng cao (AIM) công suất thấp.AIM cung cấp 40 đầu vào đúng và bổ sung cho mỗi Khối chức năng.Các khối chức năng bao gồm một PLA 40 x 56 thuật ngữ P và 16 macrocell chứa nhiều bit cấu hình cho phép các chế độ hoạt động kết hợp hoặc đã đăng ký.Ngoài ra, các thanh ghi này có thể được đặt lại hoặc đặt trước trên toàn cầu và được định cấu hình dưới dạng flip-flop D hoặc T hoặc dưới dạng chốt D.Ngoài ra còn có nhiều tín hiệu đồng hồ, cả loại thuật ngữ sản phẩm toàn cầu và cục bộ, được định cấu hình trên cơ sở mỗi macrocell.Các cấu hình chân đầu ra bao gồm giới hạn tốc độ xoay, giữ bus, kéo lên, cống mở và nền có thể lập trình.Đầu vào kích hoạt Schmitt có sẵn trên cơ sở mỗi chân đầu vào.Ngoài việc lưu trữ các trạng thái đầu ra của macrocell, các thanh ghi macrocell có thể được cấu hình như các thanh ghi "đầu vào trực tiếp" để lưu trữ tín hiệu trực tiếp từ các chân đầu vào.Bấm giờ khả dụng trên cơ sở toàn cầu hoặc Khối chức năng.Ba đồng hồ toàn cầu có sẵn cho tất cả các Khối chức năng dưới dạng nguồn đồng hồ đồng bộ.Các thanh ghi macrocell có thể được cấu hình riêng lẻ để cấp nguồn cho trạng thái không hoặc một.Một dòng điều khiển đặt/đặt lại toàn cầu cũng có sẵn để đặt hoặc đặt lại không đồng bộ các thanh ghi đã chọn trong khi vận hành.Đồng hồ cục bộ bổ sung, tín hiệu kích hoạt đồng hồ đồng bộ, đặt/đặt lại không đồng bộ và tín hiệu cho phép đầu ra có thể được hình thành bằng cách sử dụng các thuật ngữ sản phẩm trên cơ sở mỗi macrocell hoặc mỗi Khối chức năng.Tính năng lật DualEDGE cũng có sẵn trên cơ sở mỗi macrocell.Tính năng này cho phép hoạt động đồng bộ hiệu suất cao dựa trên xung nhịp tần số thấp hơn để giúp giảm tổng mức tiêu thụ điện năng của thiết bị.CoolRunner-II 64-macrocell CPLD tương thích I/O với LVTTL và LVCMOS18, LVCMOS25 và LVCMOS33 tiêu chuẩn.Thiết bị này cũng tương thích 1,5VI/O với việc sử dụng đầu vào kích hoạt Schmitt.Một tính năng khác giúp giảm bớt sự dịch chuyển điện áp là ngân hàng I/O.Hai ngân hàng I/O khả dụng trên thiết bị macrocell CoolRunner-II 64A cho phép dễ dàng kết nối với các thiết bị 3,3V, 2,5V, 1,8V và 1,5V.

| thông số kỹ thuật: | |

| Thuộc tính | Giá trị |

| Loại | Mạch tích hợp (IC) |

| Nhúng - CPLD (Thiết bị logic lập trình phức hợp) | |

| mfr | Tập đoàn Xilinx |

| Loạt | CoolRunner II |

| Bưu kiện | Cái mâm |

| Tình trạng một phần | Tích cực |

| Loại có thể lập trình | Trong hệ thống có thể lập trình |

| Thời gian trễ tpd(1) Tối đa | 6,7 ns |

| Cung cấp điện áp - Nội bộ | 1.7V ~ 1.9V |

| Số phần tử logic/khối | 4 |

| Số lượng Macrocell | 64 |

| Số cổng | 1500 |

| Số lượng I/O | 64 |

| Nhiệt độ hoạt động | 0°C ~ 70°C (TA) |

| Kiểu lắp | Bề mặt gắn kết |

| Gói / Trường hợp | 100-TQFP |

| Gói thiết bị nhà cung cấp | 100-VQFP (14x14) |

| Số sản phẩm cơ sở | XC2C64 |

Có liên quanCÁC SẢN PHẨM

-

điện thoại

-

E-mail

-

Ứng dụng trò chuyện

-

whatsapp

whatsapp